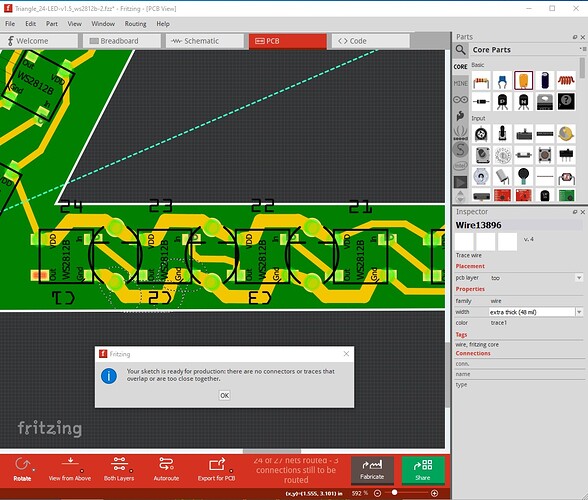

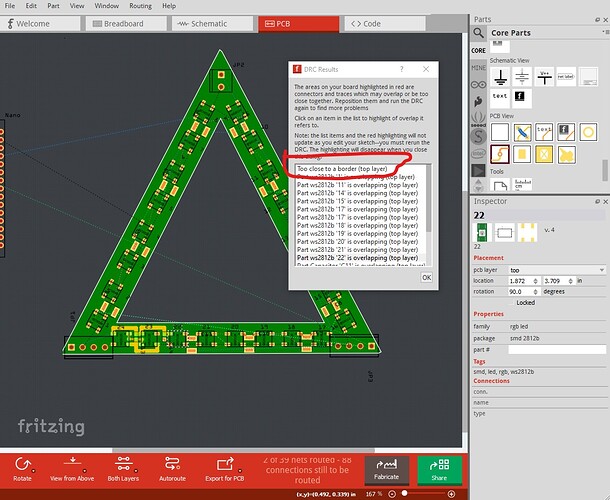

Good progress! I have made even more (although this will be a little long  .) First about the DRC errors, they are all easy to correct (although there is a serious problem in the sketch!):

.) First about the DRC errors, they are all easy to correct (although there is a serious problem in the sketch!):

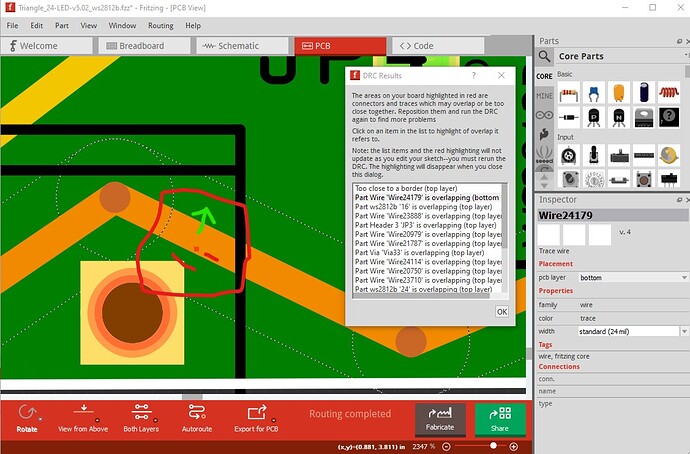

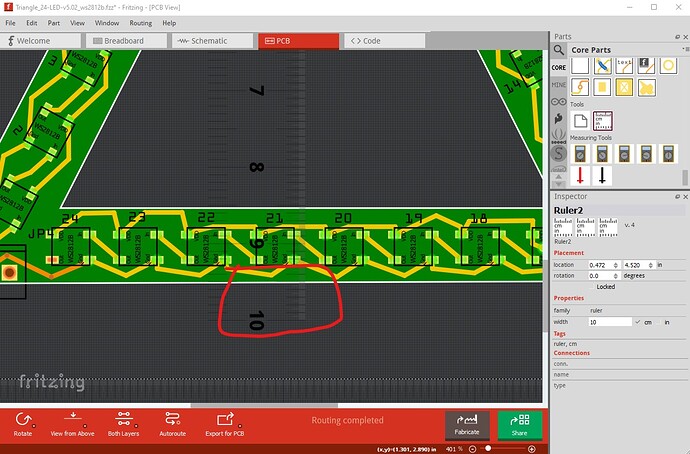

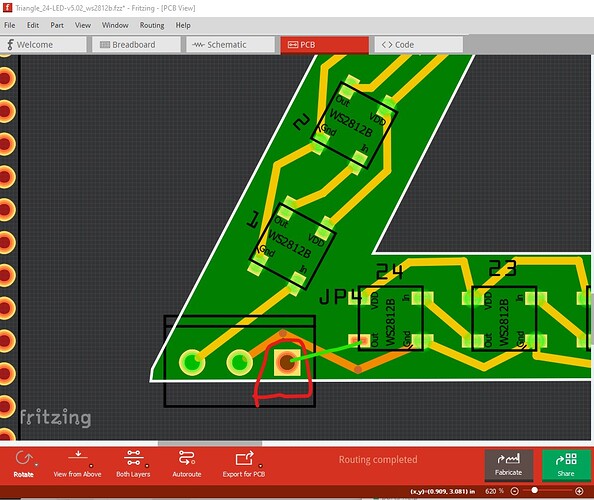

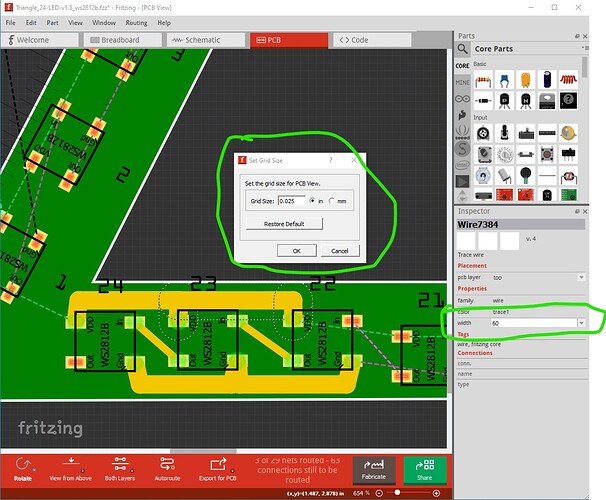

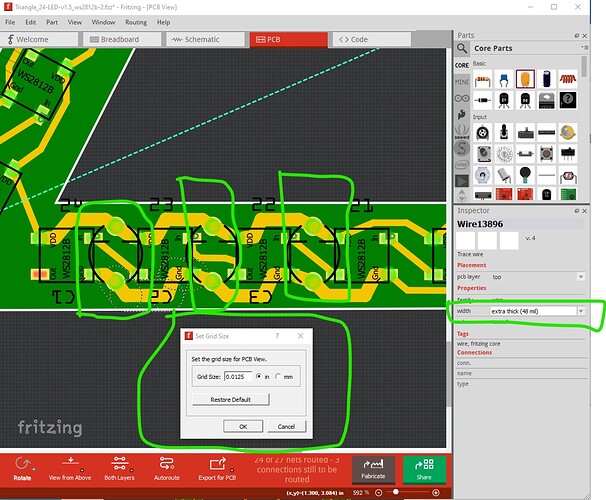

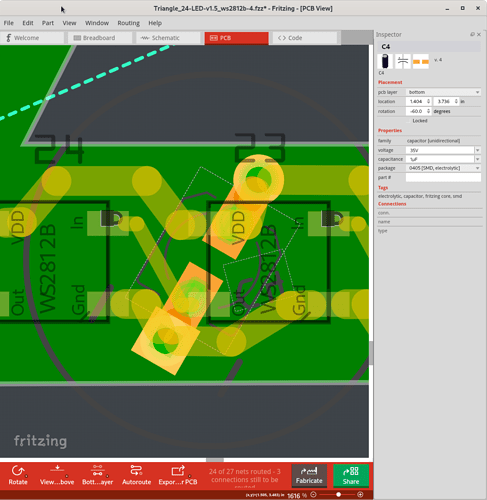

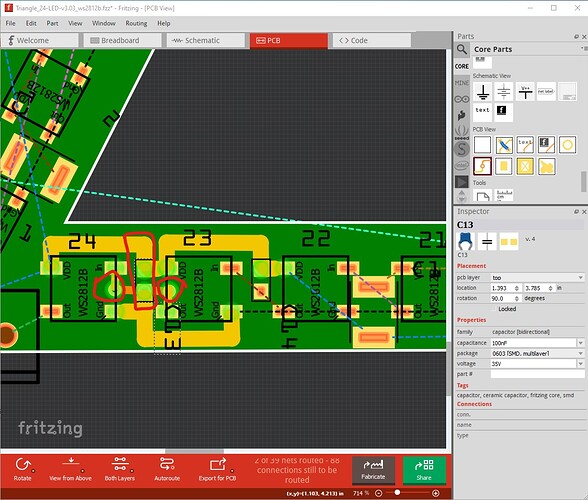

If you click on the line (as I have done here) and then zoom in on the connection it highlights, it will show you the conflict in red (possibly small and easy to miss!) move the line up a bit and the problem will go away.

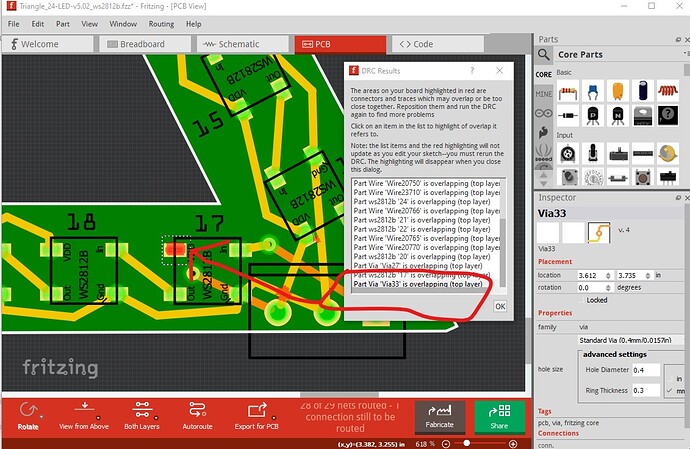

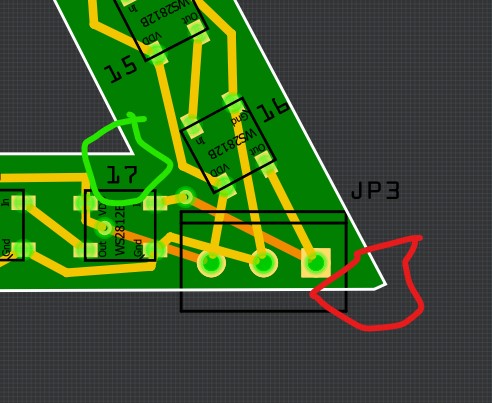

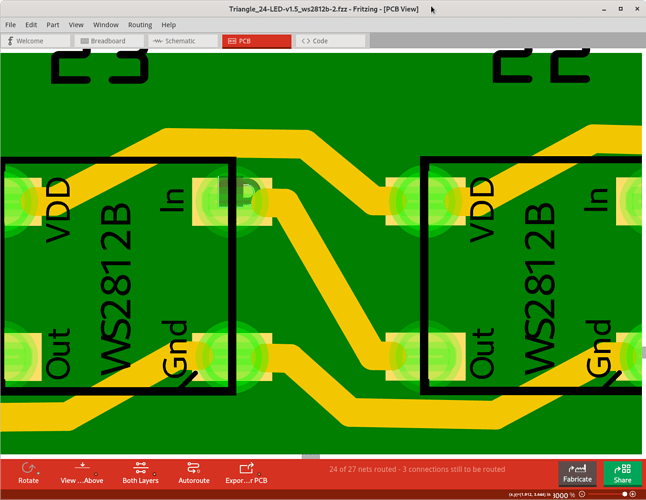

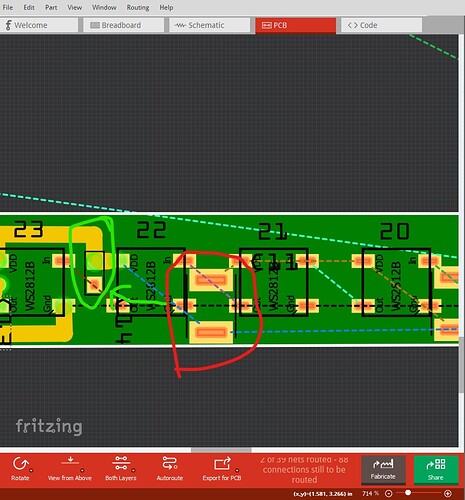

Same with this one. It is complaining about the trace circled in red being too close, moving the trace will clear it. The one circled in blue indicates a short on the top layer between VCC and GND (it will be reported somewhere else in the DRC listing as well!)

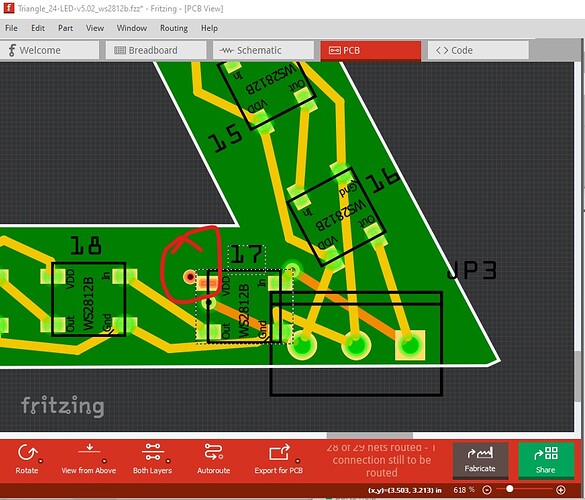

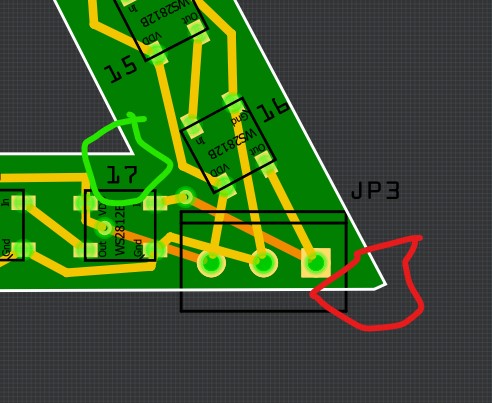

This one took me a while to find! The problem is there is a via hidden under the LED part. You can`t select it until you move the LED out of the way though (nor see it!) Here I moved the LED to show the offending via under it.

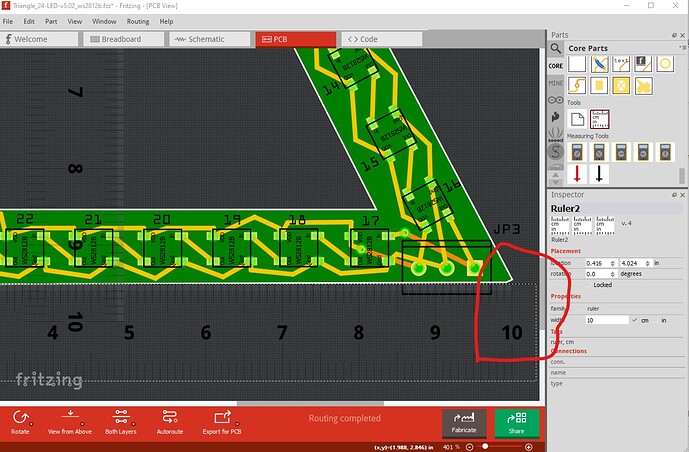

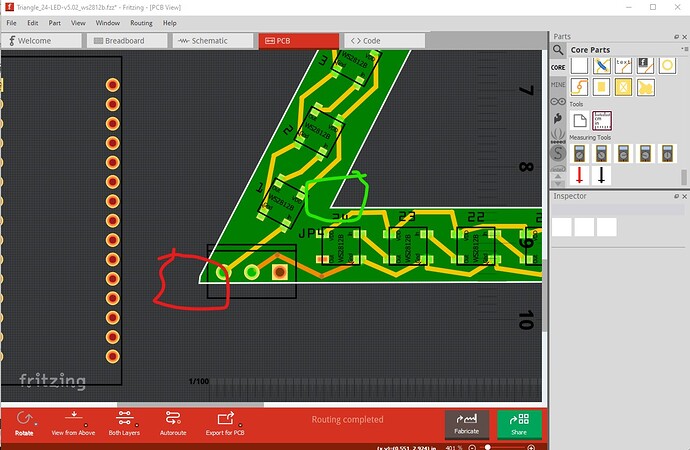

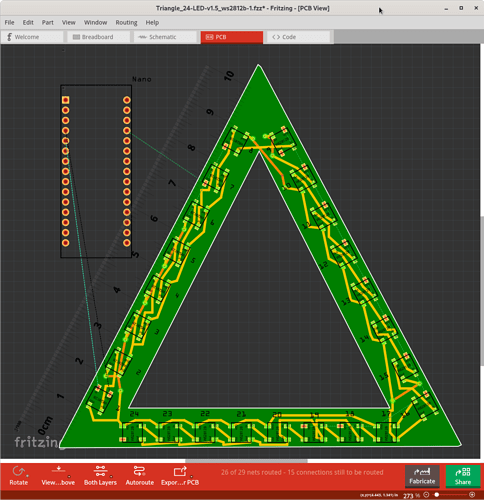

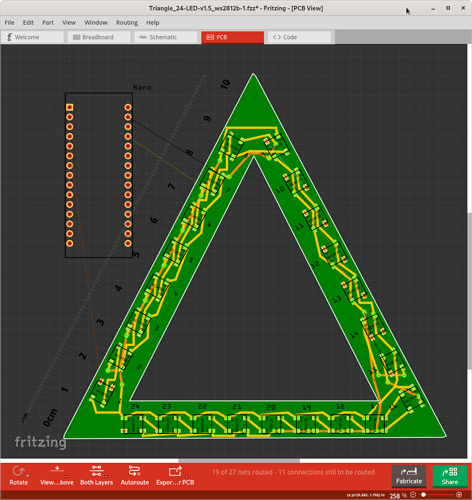

Now some layout questions (not necessarily errors, but they seem odd and may need addressing if you are not aware of them.) First the triangle is less tall ((about 9.7cm) than it is wide (almost 10cm) according to the rulers. I`d expect all three sides to be the same. Is this intended for some reason?

detail of the height difference.

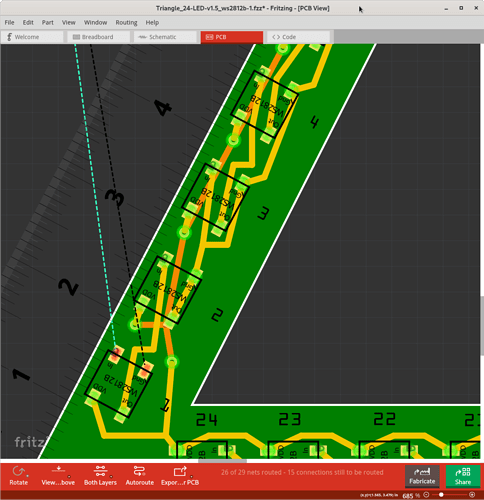

Next there look to be errors in the corners of the outline svg as shown here. The inner join (circled in green) is as I expect, the outer corner (circled in red) is misshapen. Is this intended? The board will be milled like that so the corner will be somewhat distorted I expect.

Perhaps the outline svg needs some adjustments in Inkscape to clean up the corners?

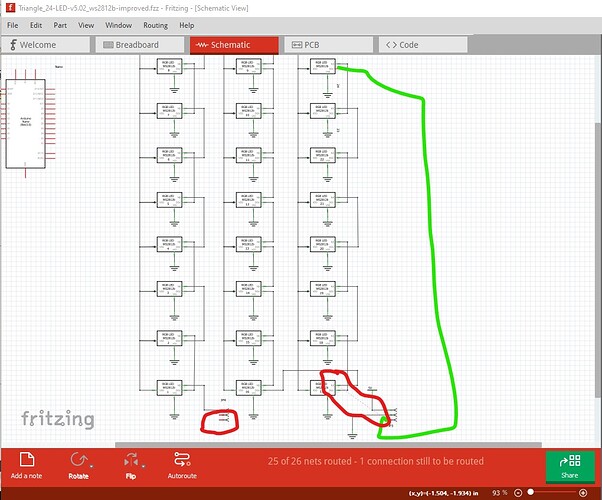

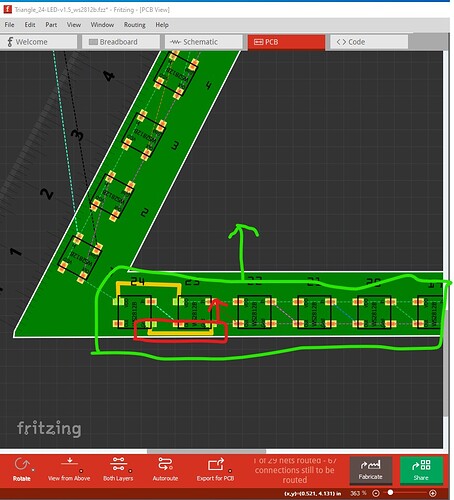

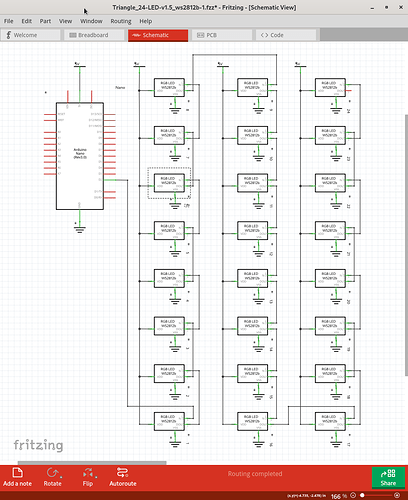

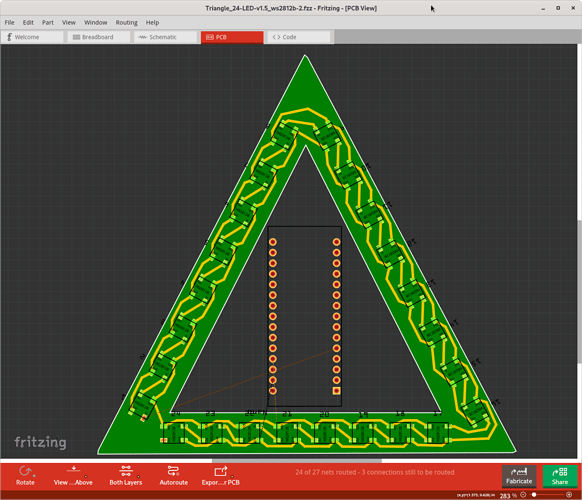

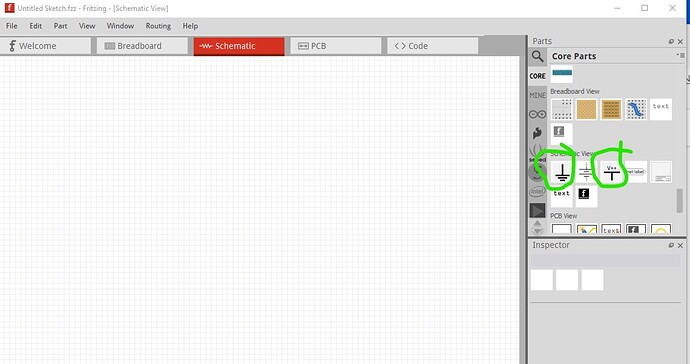

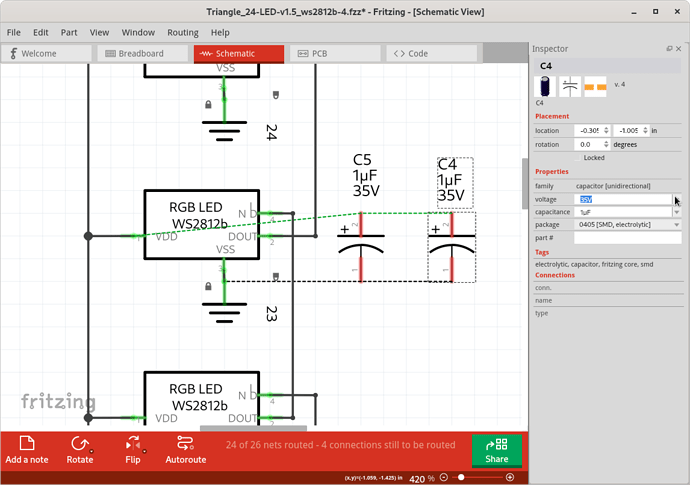

One pin on J4 has no connection. In the end by doing schematic I corrected this (you need to check that my correction is in fact what you want though! It may be that you wanted an output in the middle fot the LEDs for some reason, although it seems more likely an error!

This is what I think the error is in schematic. I think the last LED in the chain’s output should go to the header not the middle one as currently happens but there may be some reason for doing it the way it was connected.

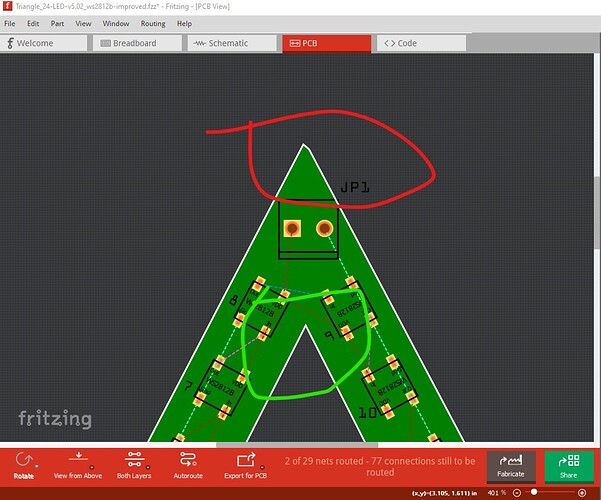

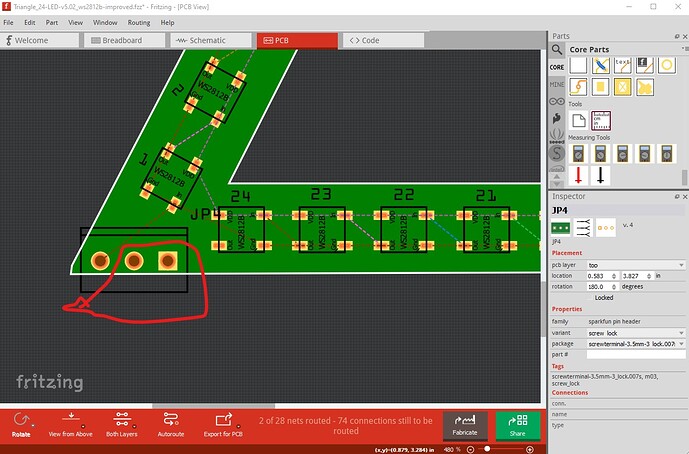

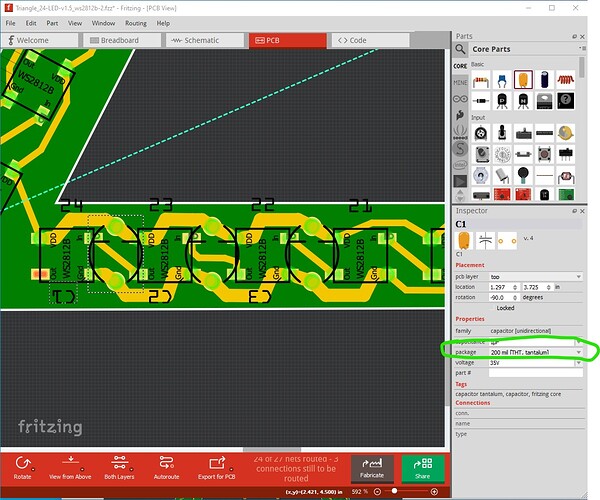

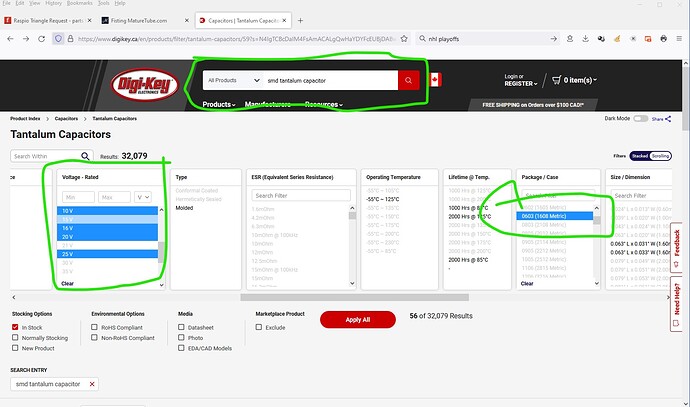

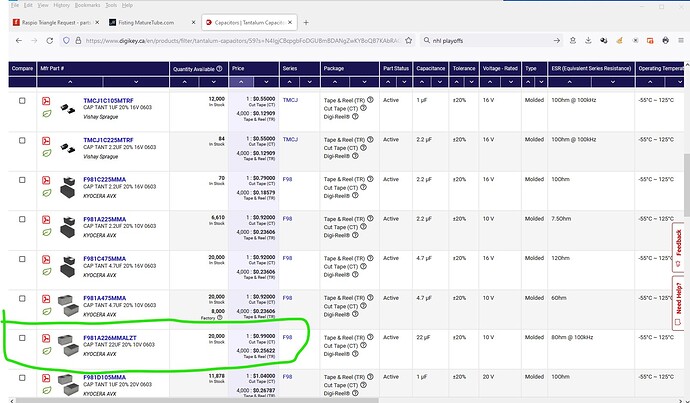

Which brings us to the serious problem. It looks like you have routing database corruption. In PCB the two pins of J4 have no rats nest lines nor connections. In schematic they are connected to VCC and ground. The best way I know of to fix this is to delete all traces in all views then reroute. To make that easier I completed schematic and completely routed it. That did not fix the problem, so I deleted all traces in schematic then re routed it completely in schematic. Then I used the rats nest lines generated from schematic in pcb to route the board manually to make sure the corruption had really cleared. That appears to be the case and as a bonus the rough route passes DRC. All these changes are contained in this sketch. I would advise checking this sketch matches what you want to do and then destroy the one that has the routing database issue (because using it probably still has the corruption which may reappear later!) I didn’t add in the bypass capacitors nor the vias for the din and dout lines but that shouldn’t be hard to do from this sketch. I would advise then making the power traces 48m instead of the current 24mils. As well JP1 seems redundant. The power is available on JP3 and JP4 as well. Again there may be a reason for it that I am not aware of.

Triangle_24-LED-v5.02_ws2812b-hoefully-not-corrupted.fzz (49.8 KB)

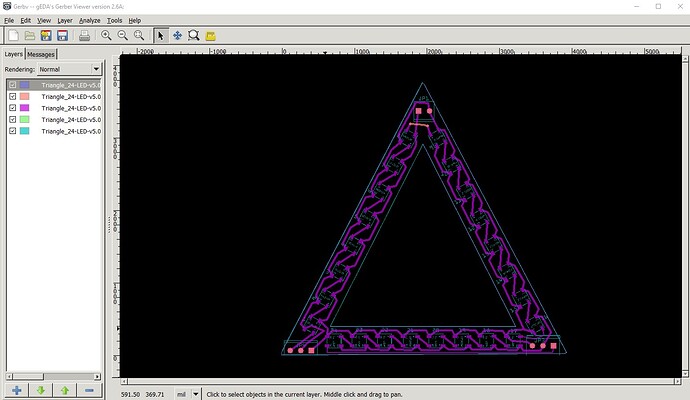

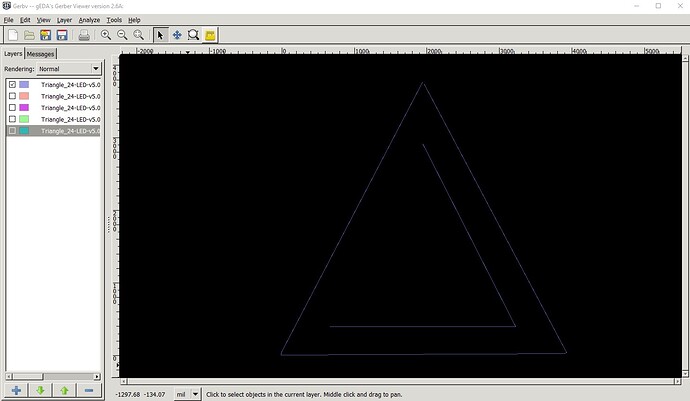

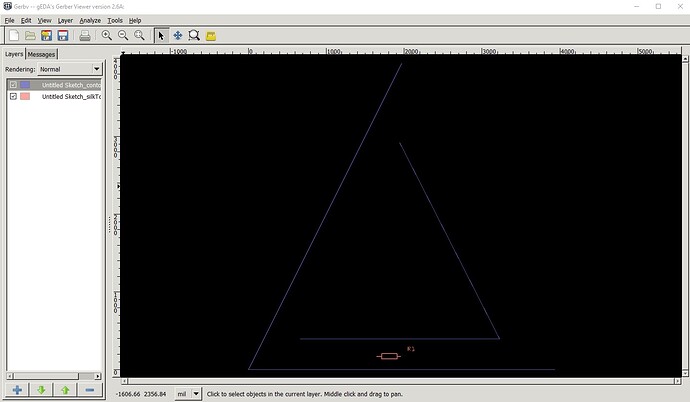

Late news: I exported pcb as geber and the gerber outline is indeed corrupted. Silkscreen looks ok (this is contour, copper0, copper1, drill and top silkscreen:

but displaying only the contour layer indicates it is corrupted and very likely won’t mill correctly.

It is missing one side of the triangle (indicating the outline svg is not correct, or there is still a Fritzing bug in path rendering (both possibilities!) Given the uneven sections in pcb view I suspect svg problems.

Peter

.) First about the DRC errors, they are all easy to correct (although there is a serious problem in the sketch!):

.) First about the DRC errors, they are all easy to correct (although there is a serious problem in the sketch!):