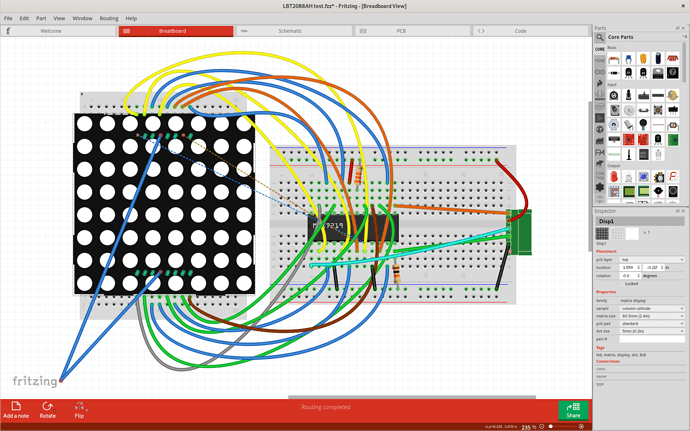

I think the pin rows of the original part were not an exact multiple of .1 inch apart. Which was why I had to initially fiddle with the breadboard positioning to get things to connect. Then the new part was at exactly 1800mils row spacing (if I did it correctly), so needed to fiddle with the positioning again. Though simply turning snap back on, and jiggling the breadboards would probably have got back in alignment.

Confirmed that with 2 “tiny” breadboards positioned at exactly 1.5 inch vertical offset, that the new 60mm LED Matrix part connects with no issues. Whether the align to grid is on or off. Tested by having align turned on, grid size 0.1, positioning the breadboards, locking the breadboards, then positioning the LED matrix both with align to grid turned off and on.

However, I just retested from scratch using the existing master branch and old LBT2088AH part. It too connected just fine, with or without align to grid, when the “tiny” breadboards were positioned and locked at 1.5 inch separation.

Back to my copy of the “LBT2088AH test.fzz” file, turn on align to grid, grid size .1, tweak the breadboard position to snap to grid, lock them, move the part off, then back on the breadboard, connects with no problems. Easily with align to grid on, a little fussy when turned off.

I probably turned it off exploring where to position the resistors. The side bus connections on the “half+” breadboard I use are offset horizontally from the core groups. Apparently by .05 inch. That makes connecting a resistor from the ground or power bus to a pin in the center groups tricky. It will often snap to the wrong side. So turn align to grid off, and carefully position where it connects properly. Or rotate to one of ±84, ±96 degrees. That is cleanest, but can break the associated connection on the schematic view.

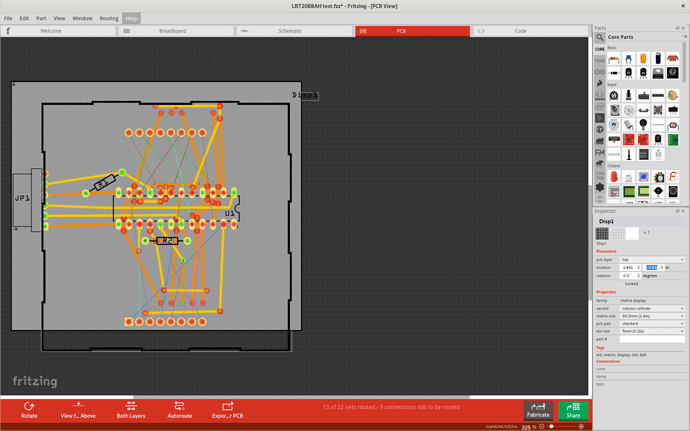

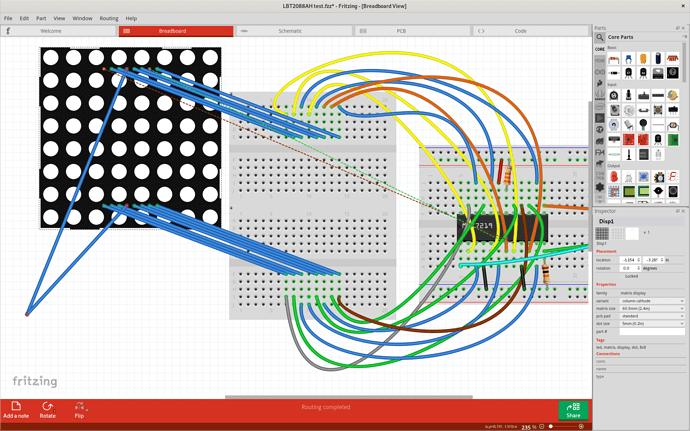

Next, I cleaned up that copy, replicating approximately what you did. Saved that, exited, switched parts libraries (actually just changed the checked out branch in that case), rebuilt the parts database, and did the update again. The breadboard view initially looks cleaner. A couple of bogus wires, and ratsnest lines, where a couple of the updated part pins did not reconnect to the breadboards.

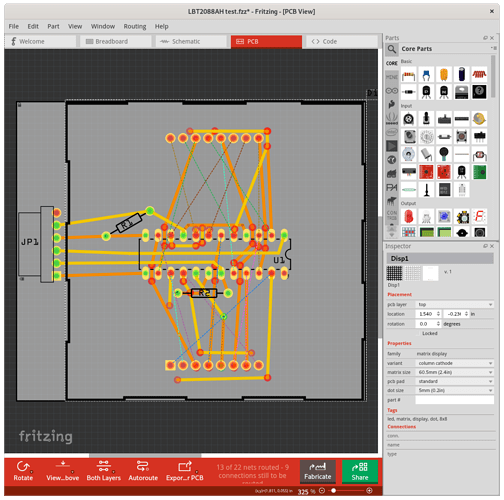

Verify that align to grid is on, set to 0.1 in, then jiggle the LED matrix part takes care of the ratsnest lines, but also show a lot more bogus wires. Moving the part away from the breadboard shows.

The initial ratsnest lines were actually the best part. A simple part move fixed them. Still not too bad. Just move the part away, delete the wires, and move it back. Or not. Deleting the wires did not create ratsnest lines. Checking the schematic view shows the connections all still in place. Moving the part back into position on the breadboards got rid of the 2 ratsnest lines again, and the breadboard view looks proper. But the pins are not really connected. Moving the matrix away from breadboard again still shows only the 2 ratsnest lines. Though schematic view looks just fine, and moving the part there drags all of the wire connections along with it. Pretty sure there is a bug in there someplace. Quite possible a nest of them.

2 pins did not connect at all on update (correctly) getting ratsnest lines to where they needed to go. 2 created bogus wires to nowhere, and the rest create bogus, almost zero length, wires where they should have just connected to the breadboard. The only pins that seem have really been connected (internal program circuit connections) were the 2 rats nest lines. Otherwise, deleting the wires should have converted to ratsnest lines.

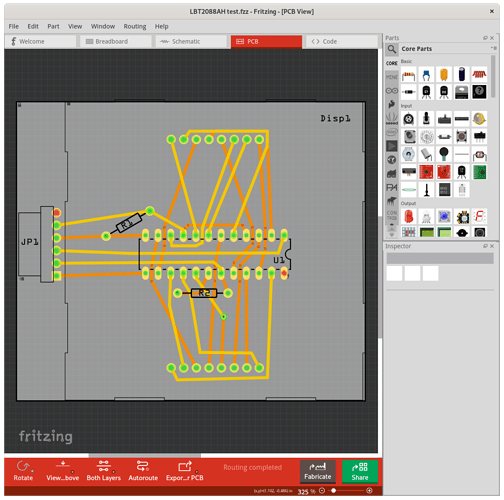

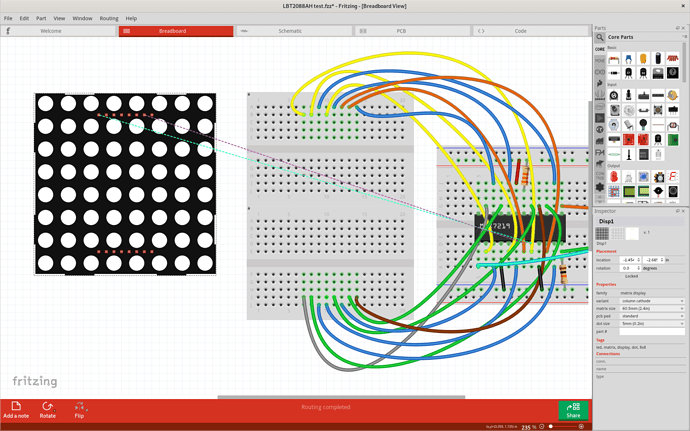

Opened your LBT2088AH-test-new-breadboard.fzz, visually saw the part move slightly on update. No visually bogus wires, or ratsnest lines, but moving the part off of the breadboards shows that all of the pins are connected to the breadboards with new wires. Deleting those wires did not create ratsnest lines. Schematic view has all of the proper connections. PCB view looks a bit better than mine, but there are a lot of red circles where traces are not connected to anything. Moving the matrix part shows that ALL of the top layer traces are disconnected. The bottom seems fine. That points to a possible copper0 / copper1 problem in the update process. Moving the part back into position did not reconnect. Moving the part away, to be able separate the connection pin and unconnected trace, I could move the open trace end and get it to reconnect. Move the part back where it belongs, and rules check passed too.

AND doing the fixes on the PCB view also brought back 5 more of the ratsnest lines on the breadboard view. 7 top layer traces were fix on PCB view. Checking pin numbers, it is all of the PCB top layer traces that have ratsnest lines on the breadboard view. 2 were there to start with.

I think we are going to need to see if we can create a (or several) smaller/simpler test case, to narrow down which conditions cause problems here. The update for LVT2088AH has to work hard on the connections. There are replacedBy keys all through it, and for several different reasons. That that all top layer traces failing is a good hint for one problem.